## Logique séquentielle

Logique dans laquelle le temps intervient dans la définition des sorties. Elle utilise la notion de mémoire de stockage (bascules, registres, etc.) alors que la logique combinatoire n'en a pas.

L'élément de base de la logique séquentielle est la bascule.

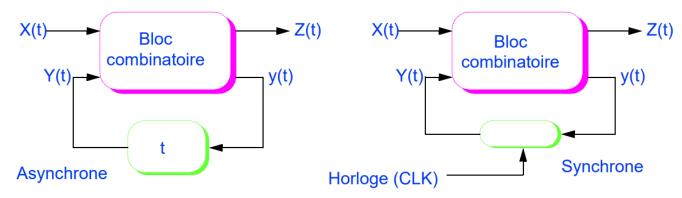

- Logique séquentielle asynchrone : les changements d'état des composants ne dépendent que du temps de réaction des composants et du temps de propagation des signaux

- Logique séquentielle synchrone : les signaux périodiques d'une horloge servent à synchroniser tous les changements d'état

- · Un système séquentiel "garde la mémoire" du passé pour déterminer son état présent

- Types de circuits

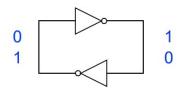

- Astable: le circuit ne possède pas d'état stable (oscillateur)

- Monostable: le circuit possède un état stable et un état fugitif de durée déterminée déclenché par un évènement particulier (trigger)

- Bistable: le circuit possède deux états stables (mémoire)

#### Les bascules

bascule (flip-flop): système permettant de mémoriser une information élémentaire.

C'est un circuit bistable. Attention, il faut un moyen de fixer l'état désiré.

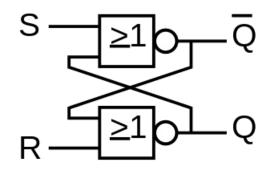

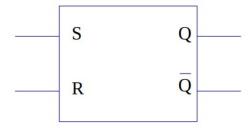

- La bascule RS : RS possède deux entrées de contrôle : Set et Reset, et n'a pas d'entrée de donnée. C'est une bascule <u>asynchrone</u>. Les deux signaux de sortie Q et  $\overline{Q}$  sont présents. Le fonctionnement de cette bascule est le suivant :

- mise à 1 de 5 (Set) : la sortie Q passe à 1 ;

- mise à 1 de R (Reset) : la sortie Q passe à 0 ;

- R = S = 0 : état mémoire : la sortie Q maintient sa valeur précédente q.

## RS avec porte NON-OU

### Table de vérité

| S | R | Q | Q | remarque      |  |

|---|---|---|---|---------------|--|

| 0 | 0 | q | q | mémoire       |  |

| 0 | 1 | 0 | 1 | mise à O      |  |

| 1 | 0 | 1 | 0 | mise à 1      |  |

| 1 | 1 | 0 | 0 | état interdit |  |

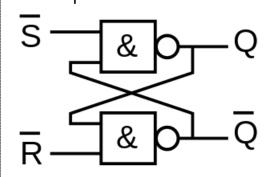

# RS avec porte NON-OU

### Table de vérité

| 5 | R | Q | Q | remarque      |

|---|---|---|---|---------------|

| 0 | 0 | 1 | 1 | état interdit |

| 0 | 1 | 1 | 0 | mise à 1      |

| 1 | 0 | 0 | 1 | mise à 0      |

| 1 | 1 | q | q | mémoire       |

## Représentation générique :

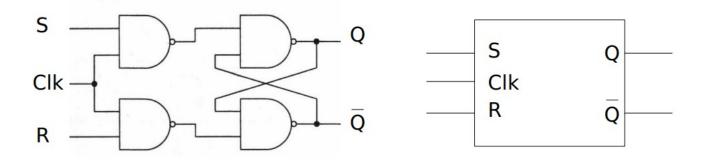

- La bascule RST : Bascule RS dans laquelle les entrées R et S ne sont prises en comptes que si elles sont en coïncidence avec un signal de commande

- bascule bloquée quand le signal de commande est à 0

- o si le signal de commande est fourni par une horloge : bascule synchrone

Table de vérité

| Н | S | R | Q | Q | remarque      |  |  |

|---|---|---|---|---|---------------|--|--|

| 0 | X | X | q | q | mémoire       |  |  |

| 1 | 0 | 0 | q | q | mémoire       |  |  |

| 1 | 0 | 1 | 0 | 1 | mise à 0      |  |  |

| 1 | 1 | 0 | 1 | 0 | mise à 1      |  |  |

| 1 | 1 | 1 | 0 | 0 | état interdit |  |  |

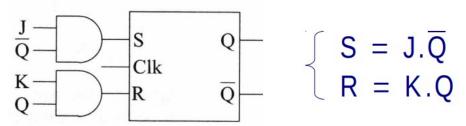

- La bascule J-K : permet de lever l'ambiguïté des bascules RST

- $\circ$  Pour J = K = 0, il y a conservation du dernier état logique Qn-1 indépendamment de l'horloge : état mémoire.

- Pour J = K = 1, le système bascule à chaque front d'horloge.

- $\circ$  Pour J différent de K, la sortie Q recopie l'entrée J et la sortie  $\overline{Q}$  recopie l'entrée K à chaque front d'horloge.

Table de vérité

Table de vérité alternative

| J | K | Q <sub>n</sub>                |  |  |

|---|---|-------------------------------|--|--|

| 0 | 0 | Q <sub>n-1</sub>              |  |  |

| 0 | 1 | 0                             |  |  |

| 1 | 0 | 1                             |  |  |

| 1 | 1 | $\overline{\mathbf{Q}}_{n-1}$ |  |  |

| <b>Q</b> <sub>n-1</sub> | J | K | $\mathbf{Q}_{\mathbf{n}}$ | remarque                                                                  |

|-------------------------|---|---|---------------------------|---------------------------------------------------------------------------|

| 0                       | 0 | X | 0                         | pour que la sortie reste à 0, il faut que J soit à 0, peu importe K.      |

| 0                       | 1 | Х | 1                         | pour que la sortie passe de 0 à 1, il faut que J soit à 1, peu importe K. |

| 1                       | Х | 1 | 0                         | pour que la sortie passe de 1 à 0, il faut que K soit à 1, peu importe J. |

| 1                       | Х | 0 | 1                         | pour que la sortie reste à 1, il faut que K soit à 0, peu importe J.      |

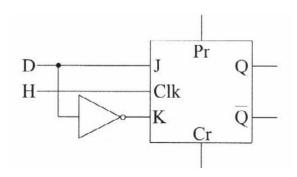

- La bascule D

- o permettent de générer un "retard" (delay) ou de stocker de l'information (latch)

- o en envoyant une donnée D sur l'entrée J et son inverse sur l'entrée K

Table de vérité

Χ

Table de vérité (optimisée)

| D | Н                    | $Q_n$            | $\overline{\mathbf{Q}}_{\mathbf{n}}$ | remarque     |

|---|----------------------|------------------|--------------------------------------|--------------|

| d | 7                    | d                | d                                    | Q recopie D  |

| Χ | 1,0,front descendant | Q <sub>n-1</sub> | $\overline{\mathbf{Q}}_{\text{n-1}}$ | mémorisation |

Rôle des entrées Pr et Cr: entrées asynchrones (lorsque Clk = 0), pour assigner l'état initial de la bascule. En fonctionnement normal, elles doivent être maintenues à 1

## Les registres

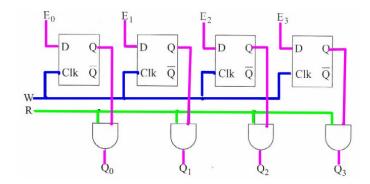

• Le registre de mémorisation : association de n bascules D pour mémoriser n bits

les entrées présentes sur E0 , E1 , E2 , E3 sont mémorisées en synchronisation avec le signal W : elles peuvent être lues sur les sorties Q0 , Q1 , Q2 , Q3 en coı̈ncidence avec le signal de validation R

Il existe d'autres type de registre, par exemple le registre à décalage. Il existe aussi des compteurs, des temporisations...